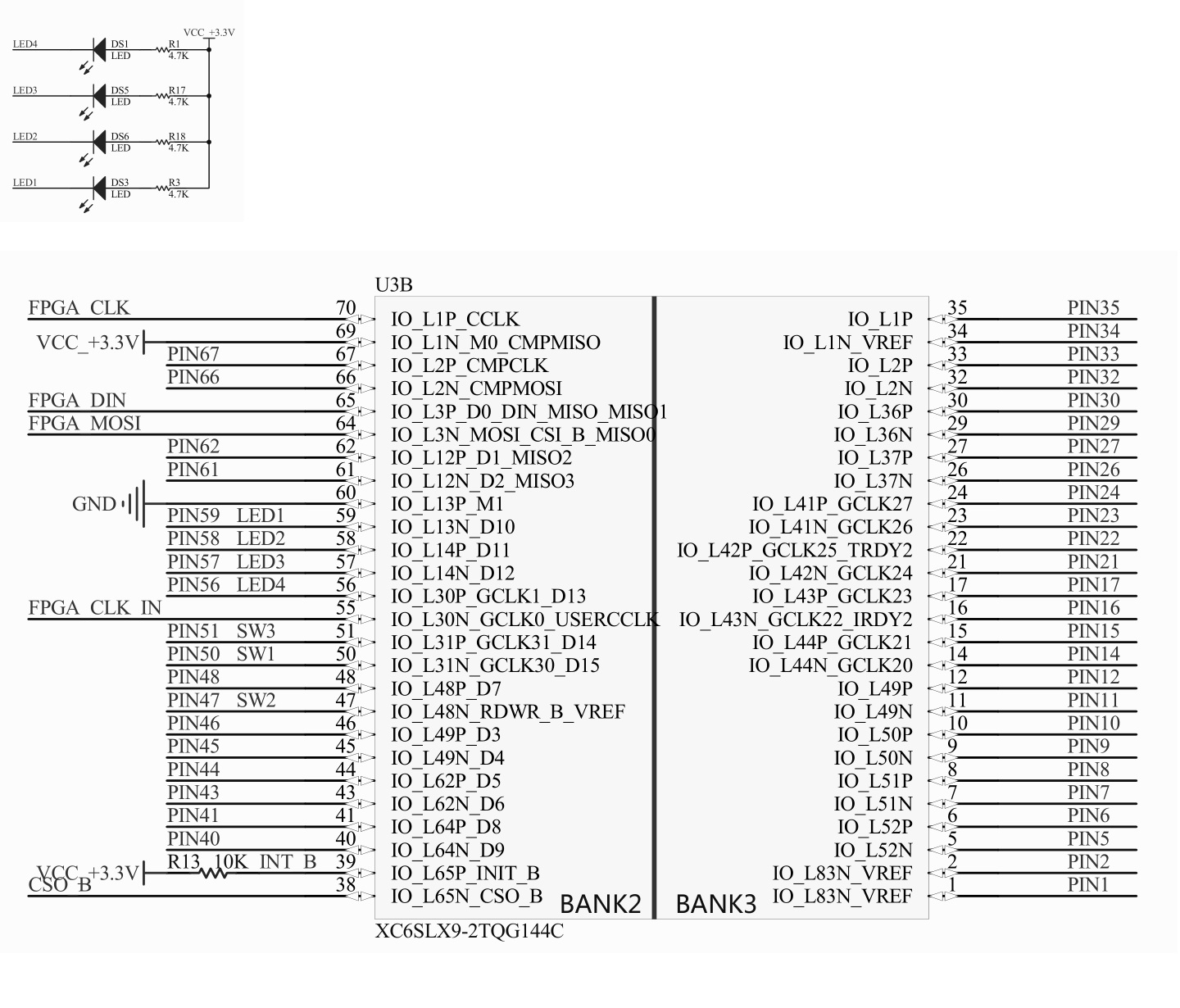

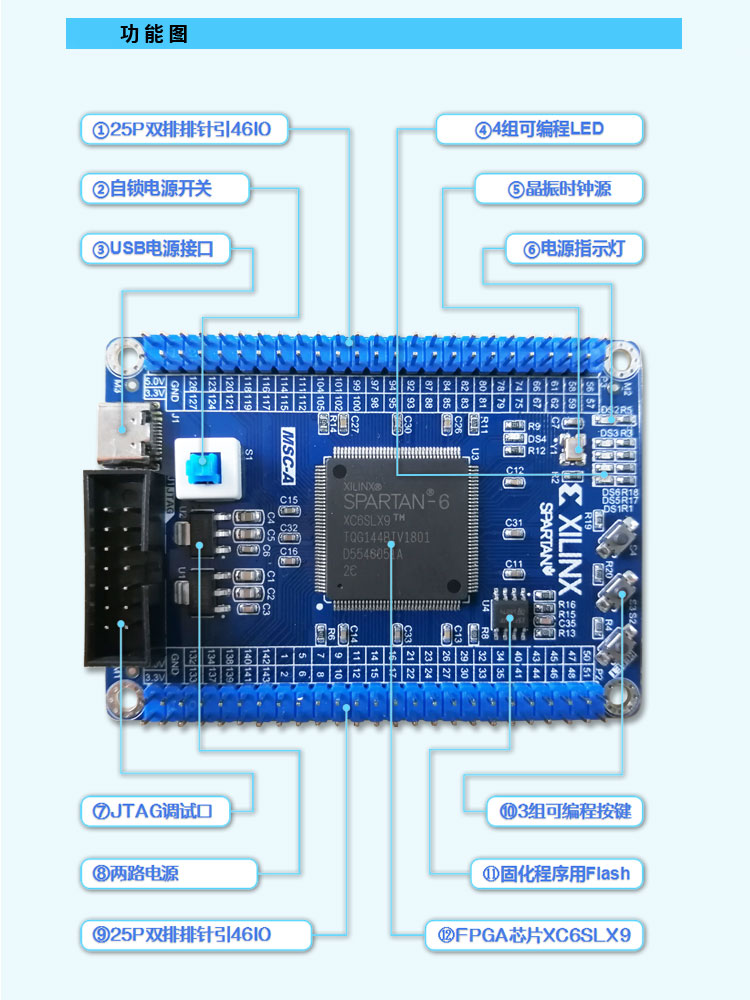

Xilinx FPGA Spartan-6 实验集合 开发板[MCS-A]

开发板

基础实验

LED 流水

配置文件

1 | |

verilog 文件1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25module led (input clk_50m, input rst_n, output reg [3:0] led);

reg [23:0] cnt;

always @(posedge clk_50m or negedge rst_n)

begin

if(0 == rst_n)

cnt <= 1'b0;

else

cnt <= cnt + 1'b1;

end

always @(posedge clk_50m or negedge rst_n)

begin

if(0 == rst_n)

led <= 4'b0001;

else if (cnt == 24'hFFFFFF)

led <= led - 1'b1;

else ;

end

endmodule

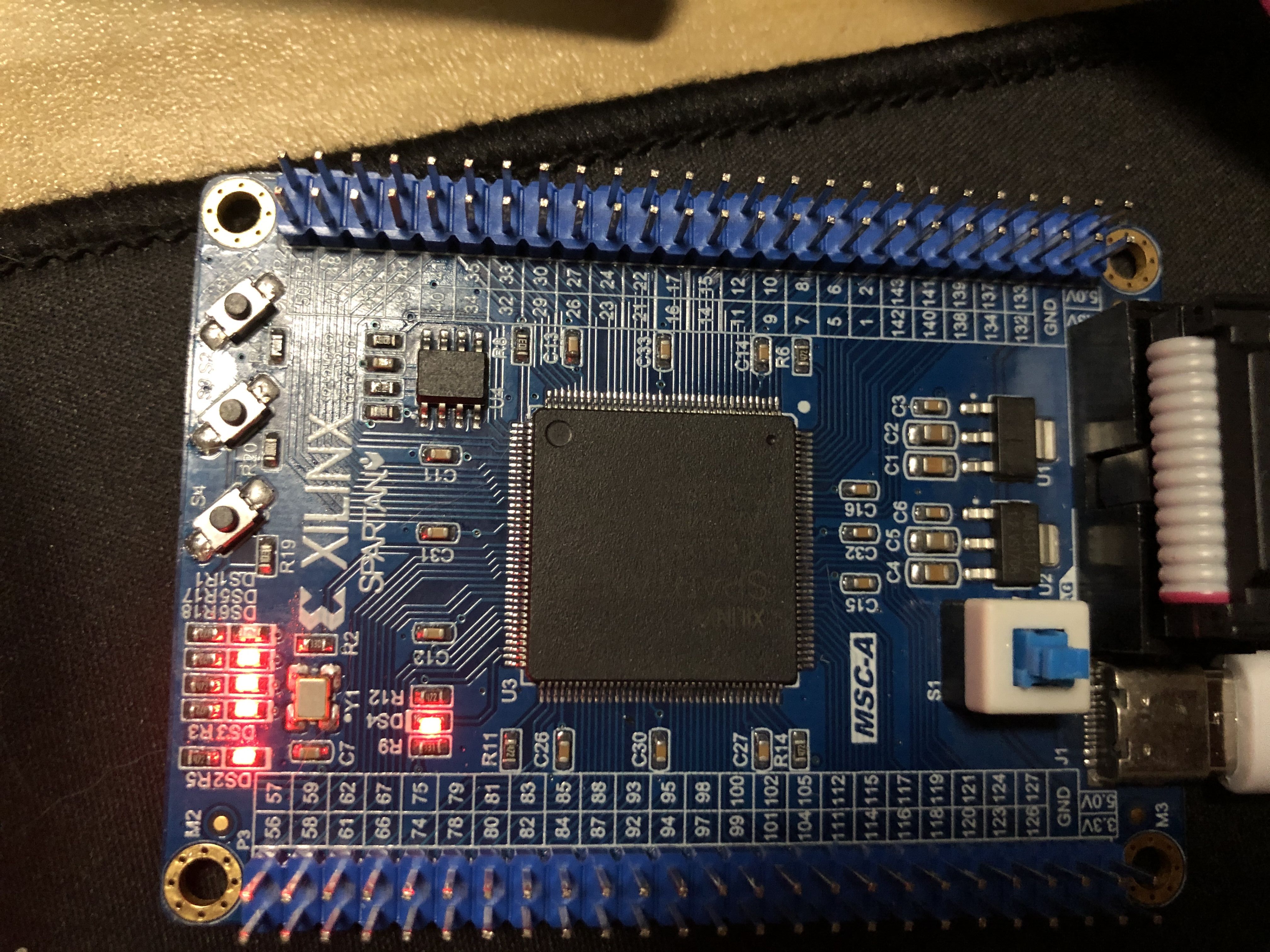

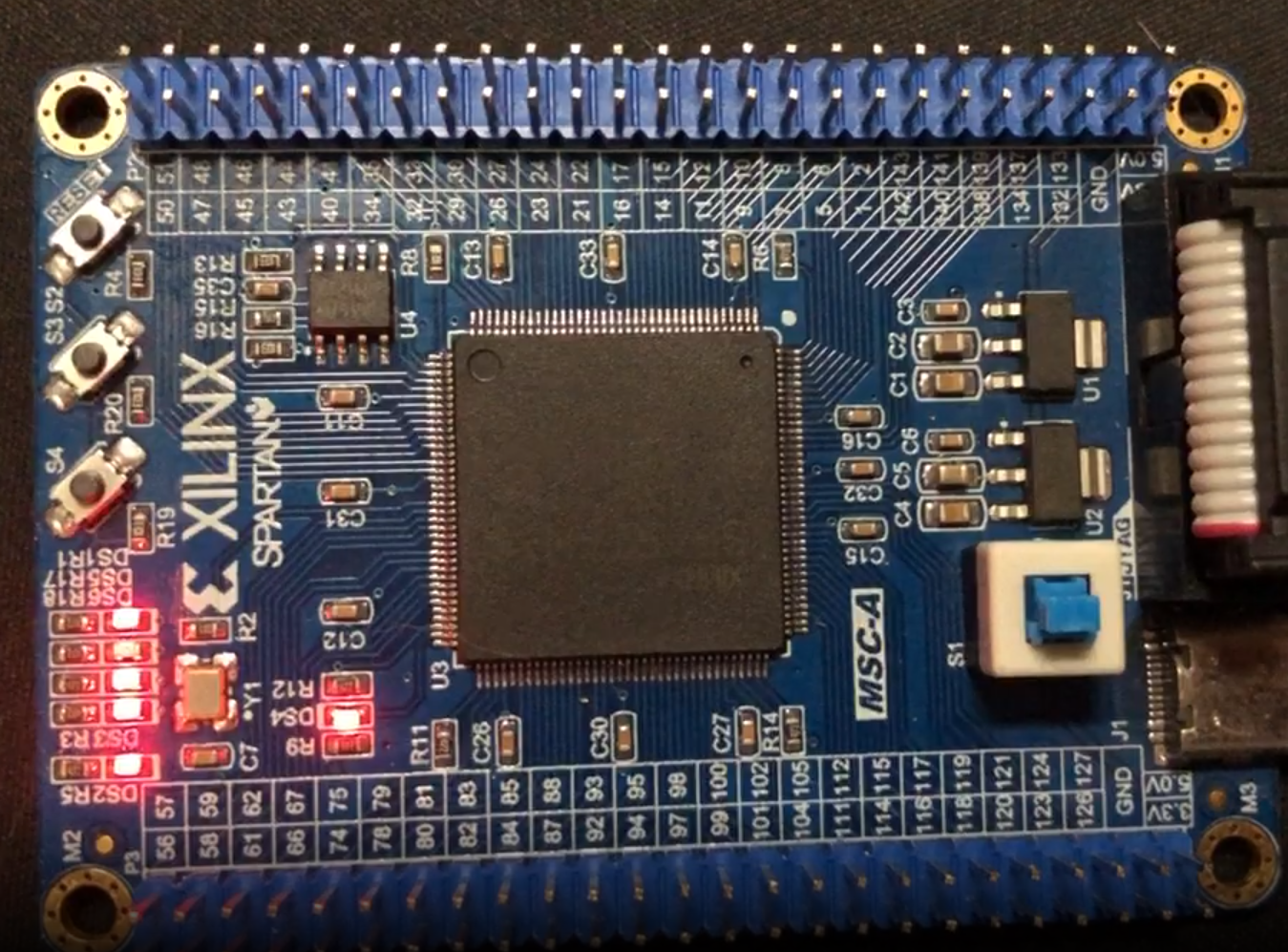

效果图

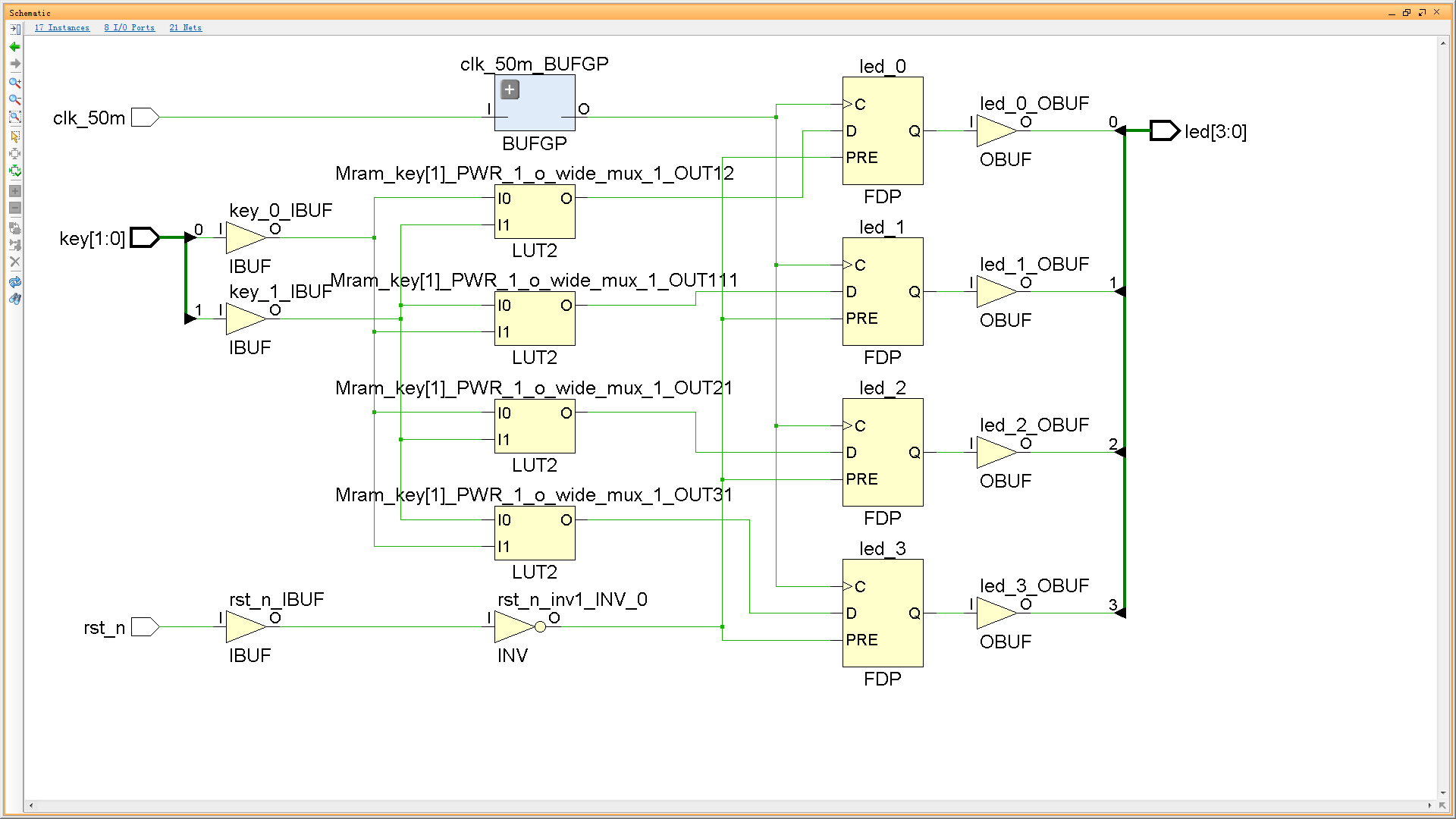

2->4 译码器

这个开发板上只有 4个LED, 为了方便, 做一个2->4译码器

配置文件1

2

3

4

5

6

7

8

9

10

11

12

13

NET "clk_50m" LOC=P55 | IOSTANDARD = LVCMOS33;

NET "rst_n" LOC=P47 | IOSTANDARD = LVCMOS33;

NET "key[0]" LOC=P50 | IOSTANDARD = LVCMOS33;

NET "key[1]" LOC=P51 | IOSTANDARD = LVCMOS33;

NET "led[0]" LOC=P56 | IOSTANDARD = LVCMOS33;

NET "led[1]" LOC=P57 | IOSTANDARD = LVCMOS33;

NET "led[2]" LOC=P58 | IOSTANDARD = LVCMOS33;

NET "led[3]" LOC=P59 | IOSTANDARD = LVCMOS33;

verilog 文件1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21module led (input clk_50m, input rst_n, input [1:0]key, output reg [3:0] led);

always @(posedge clk_50m or negedge rst_n)

begin

if(0 == rst_n)

led <= 4'b1111; //复位时 灯全灭

else

begin

case(key[1:0])

2'b11 : led <= 4'b1110;

2'b10 : led <= 4'b1101;

2'b01 : led <= 4'b1011;

2'b00 : led <= 4'b0111;

default:;

endcase

end

end

endmodule

RTL 图

bit 序列 检验

配置文件1

2

3

4

5

6

7

8

9

10

11//NET "clk_50m" LOC=P55 | IOSTANDARD = LVCMOS33;

//NET "rst_n" LOC=P50 | IOSTANDARD = LVCMOS33;

//NET "key[0]" LOC=P47 | IOSTANDARD = LVCMOS33;

//NET "key[1]" LOC=P51 | IOSTANDARD = LVCMOS33;

NET "led[0]" LOC=P56 | IOSTANDARD = LVCMOS33;

NET "led[1]" LOC=P57 | IOSTANDARD = LVCMOS33;

NET "led[2]" LOC=P58 | IOSTANDARD = LVCMOS33;

NET "led[3]" LOC=P59 | IOSTANDARD = LVCMOS33;

verolog 文件1

2

3module led (output [3:0] led);

assign led[3:0] = 4'b0001;

endmodule

效果图